# **Application Note**

**Application Note**

**Document No.: AN1114**

APM32F030x6x8 Hardware Development Guide

Version: V1.0

# 1 Introduction

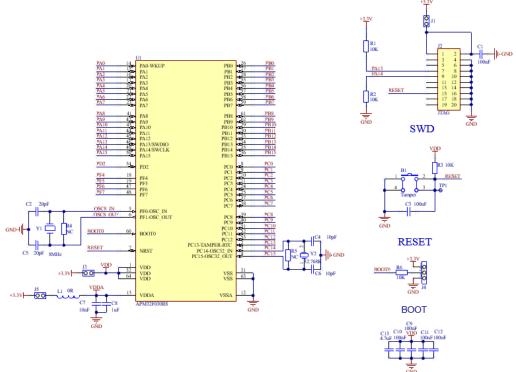

This application note is a minimum design specification for system hardware of the APM32F030x6x8 series, including power supply scheme, clock source, reset mode, startup mode settings, and debugging management.

The detailed reference design drawing is also included in this document, including descriptions of main components, interfaces, and modes.

# **Contents**

| 1   | Introduction                                | 1  |

|-----|---------------------------------------------|----|

| 2   | Power supply                                | 3  |

| 2.1 | Introduction                                | 3  |

| 2.2 | Power supply scheme                         | 4  |

| 2.3 | Power Management and Reset                  | 5  |

| 3   | Clock                                       | 8  |

| 3.1 | External clock source                       | 8  |

| 4   | Startup configuration                       | 12 |

| 5   | Debugging interface (SWJ-DP)                | 13 |

| 5.1 | Debug pin function configuration            | 13 |

| 5.2 | IO status during reset and just after reset | 13 |

| 5.3 | Recommended Debugging Interface Circuit     | 14 |

| 6   | Design Suggestions                          | 15 |

| 6.1 | PCB stacking                                | 15 |

| 6.2 | Power Supply Design                         | 15 |

| 6.3 | Grounding                                   | 16 |

| 6.4 | Clock Design                                | 16 |

| 6.5 | I/O Design                                  | 17 |

| 6.6 | EMC and EMI                                 | 17 |

| 6.7 | Reference Schematic Diagram Design          | 18 |

| 7   | Revision history                            | 19 |

# 2 Power supply

### 2.1 Introduction

The power supply is the foundation for stable operation of a system, with an operating voltage of  $2.0 \sim 3.6$ V, and 1.5V power supply can be provided by the built-in voltage regulator.

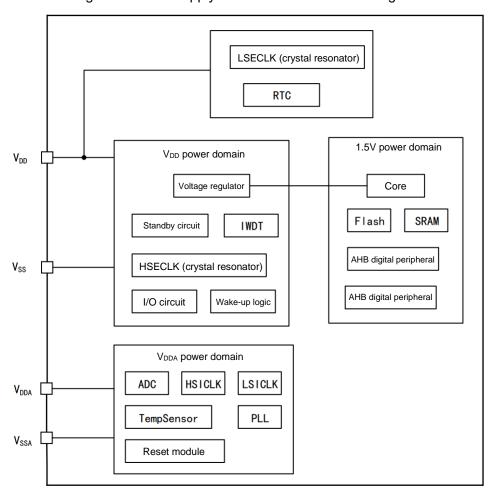

Figure 1 Power Supply Control Structure Block Diagram

### 2.1.1 Voltage regulator

Power can be supplied to 1.5V power domain in the following operating modes:

- Normal mode: In this mode, 1.5V power supply area runs at full power.

- Stop mode: In this mode, 1.5V power supply area works in low-power state, all clocks are off, and peripherals stop work

- Standby mode: In this mode, 1.5V power supply area stops power supply, and except for the standby circuit, the content of register and SRAM will be lost.

### 2.1.2 Independent ADC power supply and reference voltage

Independent ADC power supply can improve the conversion accuracy, and the specific power pins are as follows:

V<sub>DDA</sub>: Power pin of ADC

V<sub>SSA</sub>: Independent power ground pin

# 2.2 Power supply scheme

MCU LSECLK, RTC, backup register  $V_{SS}$  $\frac{V_{DD}}{I}$  4× $V_{DD}$ 4×100nF +4. 7 μ F Input Schimitt trigger Output buffer Core, Flash, Voltage regulator SRAM, I/O logic, Digital peripheral Input Schimitt trigger Output buffer  $V_{\overline{DDA}}$ RC oscillator, analog peripheral 10nF+  $V_{SSA}$  $1 \mu F$ **ADC**  $V_{REF+}$  $V_{REF}$

Figure 2 Power Supply Scheme

Pay attention to the power supply range of each power domain:

Table 1 Power Supply Scheme

| Name                               | Voltage range         | Description                                                                                     |

|------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|

|                                    |                       | Power is supplied through the V <sub>DDA</sub> /V <sub>SSA</sub> pins to the voltage regulator, |

| V <sub>DD</sub> /V <sub>SS</sub>   | 2.0∼3.6V              | standby circuit, IWDT, HSECLK, I/O (except PC13, PC14, PC15 pins)                               |

|                                    |                       | and wake-up logic                                                                               |

| V <sub>DDA</sub> /V <sub>SSA</sub> | V <sub>DD</sub> ~3.6V | Power is supplied through the VDDA/VSSA pins to the ADC, HSICLK,                                |

|                                    |                       | LSICLK, TempSensor, PLL and reset modules                                                       |

Where:

Table 2 Precautions for Power Domain

| Name             | Precautions                                                                                                      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------|--|--|

|                  | V <sub>DD</sub> must be connected to V <sub>DD</sub> power supply of an external capacitor (X 100nF ceramic      |  |  |

| V <sub>DD</sub>  | capacitor(s) <sup>(1)</sup> and a tantalum capacitor or ceramic capacitor not less than 4.7µF). V <sub>DDX</sub> |  |  |

|                  | represents that the number of $V_{DD}$ is $x$ .                                                                  |  |  |

| \/               | The V <sub>DDA</sub> pin must be connected to an external capacitor (10nF ceramic capacitor <sup>(1)</sup> +1µF  |  |  |

| V <sub>DDA</sub> | tantalum capacitor or ceramic capacitor).                                                                        |  |  |

<sup>(1)</sup> It is recommended to use the ceramic capacitors made of X7R

# 2.3 Power Management and Reset

### 2.3.1 Power-on reset and power-down reset (POR and PDR)

When the  $V_{DD}/V_{DDA}$  is lower than the threshold voltage  $V_{POR}$  and  $V_{PDR}$ , the chip will automatically remain in the reset state. The waveform diagrams of power-on reset and power-down reset are as follows. For POR, PDR, hysteresis voltage and hysteresis time, please refer to the *Datasheet*.

VPOR

VPOR

VPOR

Hysteresis voltage

Hysteresis time

Figure 3 Power-on Reset and Power-down Reset Oscillogram

### 2.3.2 Power voltage detector (PVD)

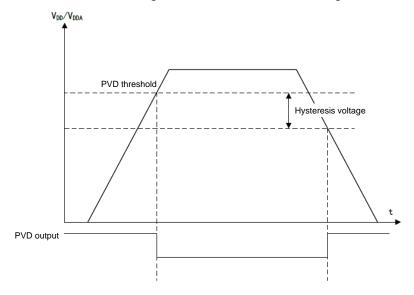

A threshold can be set for PVD to monitor whether  $_{VDD}/V_{DDA}$  is higher or lower than the threshold. If the interrupt is enabled, the interrupt can be triggered to process  $_{the}$   $_{VDD}/V_{DDA}$  exceeding the threshold in advance. The usage of PVD is as follows:

- (1) Set the PVDEN bit of the configuration register PMU\_CTRL to 1 to enable PVD

- (2) Select the voltage threshold of PVD through the PLSEL[2:0] bit of the configuration register PMU\_CTRL

- (3) The PVDOFLG bit of the configuration register PMU\_CSTS indicates whether the value of VDD is higher or lower than the threshold of PVD;

(4) When VDD/VDDA is detected to be below or above the PVD threshold, a PVD interrupt will be generated, and the threshold waveform of PVD is shown below. Please see the Datasheet for PVD threshold and hysteresis voltage.

Figure 4 PVD Threshold Oscillogram

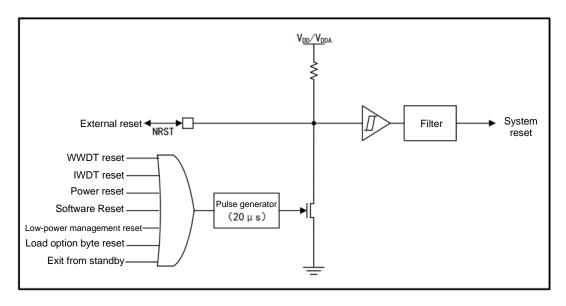

### 2.3.3 System reset

The reset source is divided into external reset source and internal reset source.

Reset source: Low level on NRST pin

(1) Window watchdog termination count (WWDT reset)

(2) Independent watchdog termination count (IWDT reset)

(3) Software reset (SW reset)

(4) Low-power management reset

(5) Load option byte reset

(6) Power reset

Table 3 Reset Source

A system reset will occur when any of the above events occurs. Besides, the reset event source can be identified by viewing the reset flag bit in RCM\_CSTS (control/status register).

### 2.3.3.1 System reset circuit

The reset source is used in the NRST pin, which remains low in reset process. The internal reset source generates a delay of at least 20µs pulse on the NRST pin through the pulse generator, which causes the NRST to generate reset; the external reset source directly pulls down the NRST pin level to generate reset.

The system reset circuit is shown in the following figure:

Figure 5 System Reset Circuit

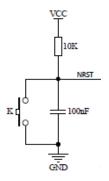

### Recommend external reset circuit

Figure 6 External Reset Circuit

### 3 Clock

The clock sources of the whole system are: HSECLK, LSECLK, HSICLK, LSICLK and PLL. For the characteristics of the clock source, please refer to the relevant chapter of "Electrical Characteristics" in the datasheet.

LSECLK HSICLK 1201 USBD\_SOF HS I CLK48 SPI1/I2S1 SPI2/I2S2 HS I CLK48 HS1CLK48 HSICLK AHB/Core/ Memory/DMA HSICLK PLLMUL ×2, ×3 ····×16 PLLDIA PLLCLK HSICLK 8MHz SYSCLK /1. 2---HCI K /8 System Timer /512 /1, /2, /4, /8, /16 **PCLK** ► APH peripheral TMR1/2/3/ 6/7/14/15 /16/17 HSECLK OSC\_OUT **HSECLE** ×1, ×2 OSC 4-32MHz OSC\_IN HSECLK /32 SYSCLK LSECLK USART1 /USART2 RTC HSICLK LSICLK LSECLK HSICLK14 RC 14MHz HSICLK14 ADC asynchronous signal input HS1CLK48 USBD PLLCL 0SC32\_0UT LSECLK LSECLK OSC 0SC32\_IN 32. 768kHz LSICLK LSICLK LSECLK 40kHz CEC LSICLK | IWDT HSICLK /244 -PLLCLK -SYSCLK -HSECLK Flash programming interface **HSICLK** Clock output /1, /2 --/128 HS I CLK MCO HSTCLK14 HS1CLK48 -LSICLK LSECLK ►TMR14

Figure 7 Clock Tree

### 3.1 External clock source

The external clock signal includes HSECLK (high-speed external clock signal) and LSECLK (low-speed external clock signal).

### There are two kinds of external clock sources:

- External crystal/ceramic resonator

- External clock of user

The hardware configuration of the two kinds of clock sources is shown in the figure below.

External clock

Crystal/Ceramic resonator

Hardware configuration

APM32F030

OSC\_IN OSC\_OUT

External clock source

APM32F030

OSC\_IN OSC\_OUT

Crystal/Ceramic resonator

Figure 8 HSECLK/LSECLK Clock Source Hardware Configuration

### Note:

- (1) In order to reduce the distortion of clock output and shorten the startup stabilization time, the crystal/ceramic resonator and load capacitor must be as close to the oscillator pin as possible. The value of the matching capacitance ( $C_{L1}$ ,  $C_{L2}$ ) must be adjusted according to the selected oscillator.

- (2) The load capacitor CL follows the formula of:  $C_{L=C_{L1}} \times C_{L2} / (C_{L1} + C_{L2}) + C_S$ .  $C_S$  is related capacitance of PCB and MCU pins, and the typical value is between 2pF and 10pF.

### 3.1.1 HSECLK high-speed external clock signal

The HSECLK clock signal has two kinds of clock sources: HSECLK external crystal/ceramic resonator and HSECLK external clock.

Table 4 Clock Source Generating HSECLK

| Name                  | Description                                                                  |

|-----------------------|------------------------------------------------------------------------------|

|                       | Provide clock to the MCU through OSC_IN pin.                                 |

|                       | The signal can be generated by ordinary function signal transmitter (in      |

| External clock source | debugging), crystal oscillator and other signal generators; the waveform can |

| (HSECLK bypass)       | be square wave, sine wave or triangle wave with 50% duty cycle, and the      |

| (113ECER Dypass)      | maximum frequency is up to 32MHz.                                            |

|                       | In hardware connection, it must be connected to the OSC_IN pin and the       |

|                       | OSC_OUT pin must be suspended.                                               |

| External              | The clock is provided to MCU by the resonator, and the resonator includes    |

| Name             | Description                                                                         |

|------------------|-------------------------------------------------------------------------------------|

| crystal/ceramic  | crystal resonator and ceramic resonator. The frequency range is 4-32MHz.            |

| resonator        | OSC_IN, OSC_OUT is required to connect the resonator,                               |

| (HSECLK crystal) | and it can be turned on and off by setting the HSEEN bit in RCM_CTRL in             |

|                  | the clock control register.                                                         |

|                  | Regarding the size of the external matching capacitor, please                       |

|                  | refer to the formula: $C_{L1} = C_{L2} = 2^*(C_L - C_S)$ , where $C_S$ is the stray |

|                  | capacitance of the PCB and MCU pins, and the typical value is 10pF. When            |

|                  | selecting an external high-speed crystal resonator, it is recommended to            |

|                  | select the one with a load capacitance of around 20pF, so that the external         |

|                  | matching capacitors (1) CL1 and CL2 only need to have a capacitance                 |

|                  | value of 20pF, and the PCB should be as close as possible to the crystal            |

|                  | oscillator pins.                                                                    |

### Note:

(1) It is recommended to use the temperature compensation capacitors made of NPO (COG) for the matching capacitor of the crystal oscillator.

### 3.1.2 LSECLK low-speed external clock signal

The LSECLK clock signal has two kinds of clock sources: LSECLK external crystal/ceramic resonator and LSECLK external clock.

Table 5 Clock Source Generating LSECLK

| Name                     | Description                                                                               |  |

|--------------------------|-------------------------------------------------------------------------------------------|--|

|                          | The clock is provided to MCU by OSC32_IN pin.                                             |  |

|                          | The signal can be generated by ordinary function signal transmitter (in                   |  |

|                          | debugging), crystal oscillator and other signal generators; the waveform can              |  |

| External clock source    | be square wave, sine wave or triangle wave with 50% duty cycle, and the                   |  |

| (LSECLK bypass)          | signal frequency needs to be 32.768kHz.                                                   |  |

| (LOLOLK Dypass)          | For hardware connection, it must be connected to OSC32_IN pin, ensuring                   |  |

|                          | OSC32_OUT pin is suspended; for MCU configuration, the user can select                    |  |

|                          | this mode by setting LSEBCFG and LSEEN bits in RCM_BDCTRL (backup                         |  |

|                          | domain control register).                                                                 |  |

|                          | The clock is provided to MCU by the resonator, and the resonator includes                 |  |

|                          | crystal resonator and ceramic resonator. The frequency is 32.768kHz.                      |  |

|                          | When needing to connect OSC32_IN and OSC32_OUT to the resonator,                          |  |

| External crystal/ceramic | it can be turned on and off through the LSEEN bit in RCM_BDCTRL.                          |  |

| resonator                | Regarding the size of the external matching capacitor, please refer to the                |  |

| (LSECLK crystal)         | formula: $C_{L1} = C_{L2} = 2^*(C_L - C_S)$ , where $C_S$ is the stray capacitance of the |  |

|                          | PCB and MCU pins, and the typical value is 5pF. When selecting an                         |  |

|                          | external crystal resonator, it is recommended to select the one with a load               |  |

|                          | capacitance of around 10pF, so that the external matching capacitors (1)                  |  |

Document No.: AN1104

| ĺ | 014 1010 1 111 2 1 140 5 14 505                                              |

|---|------------------------------------------------------------------------------|

|   | CL1 and CL2 only need to have a capacitance value of 10pF, and the PCB       |

|   | should be as close as possible to the crystal oscillator pins during layout. |

### Note:

(1) It is recommended to use the temperature compensation capacitors made of NPO or COG for the matching capacitor of the crystal oscillator.

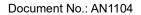

# 4 Startup configuration

APM32F MCU series realizes a special mechanism. By configuring the BOOT pin parameter and the nBOOT1 bit in FMC\_OBCS, there are three different startup modes, namely, the system can not only start from Flash memory or system memory, but also start from the built-in SRAM. The memory selected as the start zone is determined by the selected startup mode.

| Startup mode selection pin |       | Startup mode                    | Access methods                                                                                                                                                                           |

|----------------------------|-------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| воото                      | BOOT1 | -                               |                                                                                                                                                                                          |

| 0                          | X     | Main flash<br>memory<br>(Flash) | The main flash memory is mapped to the boot space, but it can still be accessed at its original address, that is, the contents of the flash memory can be accessed in two address areas. |

| 1                          | 0     | System memory                   | The system memory is mapped to the boot space (0x0000 0000), but it can still be accessed at its original address.                                                                       |

| 1                          | 1     | Built-in SRAM                   | SRAM can be accessed only at the starting address.                                                                                                                                       |

Table 6 Startup Mode Configuration and Access Mode

- The user can select the startup mode after reset by setting the states of BOOT0 pin and Boot option byte.

- BOOT pin should keep the startup configuration required by user in standby mode.

When exiting the standby mode, the value of boot pin will be latched.

- If you choose to start from built-in SRAM, you must use NVIC's exception table and offset register to remap the vector table to SRAM when writing the application code.

Figure 9 Recommended BOOT Circuit Design

# 5 Debugging interface (SWJ-DP)

The product only supports serial debugging interface (SW-DP).

Table 7 Debugging Interface

| Name  | Description                                                             |

|-------|-------------------------------------------------------------------------|

| SW-DP | SW-DP interface provides 2-pin (data + clock) interface for AHB module. |

# 5.1 Debug pin function configuration

- Realize the on-line programming and debugging of the chip.

- Use KEIL/IAR and other software to implement on-line debugging, downloading and programming.

- Flexible implementation of production of bus-off programmer.

Table 8 Pin Function Configuration

|               | Configured as dedicated pin for | I/O port assignment of SWJ interface |                |

|---------------|---------------------------------|--------------------------------------|----------------|

| SWJ- CFG[2:0] | debugging                       | PA13/<br>SWDIO                       | PA14/<br>SWCLK |

| Others        | Disable                         |                                      |                |

| 100           | SW-DP interface is disabled     | Release                              |                |

| 010           | SW-DP interface is enabled      | Special                              | Special        |

| 001           | All SWD pins                    | Special                              | Special        |

| 000           | All SWD pins Reset state        | Special                              | Special        |

# 5.2 IO status during reset and just after reset

If the multiplexing function is not enabled during and after GPIO reset, the I/O port will be configured as floating input mode, and in such case, the pull-up/pull-down resistor is disabled in input mode. After reset, the SWD pin is set in the input pull-up or pull-down mode, and the specific configuration is as follows:

- PA14: SWCLK is set to pull-down mode;

- PA13: SWDIO is set to pull-up mode;

# 5.3 Recommended Debugging Interface Circuit

### Recommended SWD interface reference design:

VDD 10K APM32F030 **SWD** VDD VDD VDD **PA13 SWDIO PA14 SWCLK NRST RESET GND GND** 10K

Figure 10 SWD Interface Circuit

### Note:

(1) The reference design for the SWD interface is to add an external pull-up resistor and pull-down resistor to the SWDIO and SWCLK pins, which can enhance the anti-interference ability of downloading and debugging. If these two pins are multiplexed for other functions, please evaluate the impact of the pull-up and pull-down resistors and make adjustments according to the actual situation.

# 6 Design Suggestions

### 6.1 PCB stacking

- Number of layers: It is recommended to use the multi-layer design to ensure independent GND and power layers, which can better ensure signal integrity and enhance shielding effect. However, considering the costs, users can reduce the number of stacking layers while ensuring good grounding and power supply.

- Signal and formation: The signal layer should be adjacent to the formation. This

helps to reduce the electromagnetic interference and the loop area of the signal

path, and can serve as a reference plane for the signal.

- Power supply and formation: The power supply layer should be separated from the formation.

### 6.2 Power Supply Design

- Stable power input: Ensure stable power supply, and the power pins should provide good filtering processing. When connecting to large capacitive or inductive loads, ensure the stability of power supply design and avoid affecting the power supply stability of the MCU. The filtering capacitors, soft start circuits, surge protection circuits, etc. can be added to ensure the stability of the input power supply.

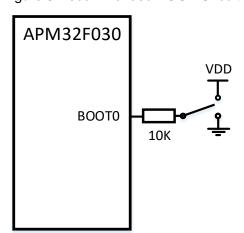

- Decoupling capacitors: Place one or more 100nF decoupling capacitors at each VDD pin near the chip (depending on the application). (V<sub>DD</sub>/V<sub>DDA</sub>) Decoupling capacitor is placed closest to the relevant pins to produce the best effect.

Figure 11 Recommended Power Pin Decoupling Capacitor Layout Design

Power supply wiring: It is recommended that the power supply wiring should be wide and short enough to reduce the voltage drop and the influence of parasitic parameters.

### 6.3 Grounding

- Single-point grounding: In low-frequency circuits or circuits with not high noise requirements, adopting single-point grounding can avoid formation of ground loop.

In such case, all grounding points should be connected to a common grounding point, which is usually the negative pole of the power supply or some grounding plane on the circuit board.

- Multi-point grounding: In high-frequency circuits or high-current circuits, usually

multi-point grounding is used. The grounding of each component or function

module is directly connected to the nearest grounding plane, which can reduce

the impedance of the ground wire, and reduce the noise and electromagnetic

interference.

- Separation of analog from digital ground: If the MCU processes the analog and digital signals simultaneously, the analog ground and digital ground should be processed separately. This can be achieved by physically separating two ground planes and merging them at a certain point to connect them to the main ground, which can reduce the interference of digital noise with the analog signals.

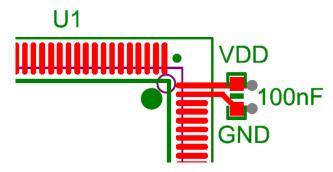

### 6.4 Clock Design

- Crystal oscillator selection: Choose an appropriate crystal oscillator and ensure it meets the operating frequency and stability requirements of the MCU.

- Wiring suggestions: Clock signal wiring should be as short as possible and be away from strong interference signals such as high current and high-speed signal lines. It is recommended to use package processing to enhance the shielding effect.

- Layout suggestions: The crystal oscillator circuit should be placed close to the chip and on the same layer with the chip, and to reduce the interference. It is best to ensure a complete ground plane below the entire crystal oscillator circuit.

Figure 12 Recommended Clock Pin Layout Design

# 6.5 I/O Design

- I/O configuration: Correctly configure the modes of I/O ports, such as input, output, pull-up and pull-down, and open-drain mode.

- Protection: For externally connected I/O ports, consider adding the voltage protection (TVS/ESD tube) and series resistor.

- Some pins connected to the internal analog channels are sensitive to negative pressure. In extreme cases, the negative pressure may cause the MCU system to reset. It is recommended to conduct IO filtering and protection design during use.

### 6.6 EMC and EMI

- Layout: Consider the design of electromagnetic compatibility (EMC) and electromagnetic interference (EMI), and the layout should be reasonable. For example, when laying out MCU circuits, they should be kept away from high-power and strong interference sources, and the loop area should be reduced during wiring. Low-frequency small signals should be kept away from high-frequency signals and high-current circuits.

- Shielding: Use shielding and reasonable grounding strategies for sensitive and high-speed circuits.

# 6.7 Reference Schematic Diagram Design

Figure 13 Reference Schematic Diagram

# 7 Revision history

# Table 9 Document Revision History

| Date       | Version | Revision History |

|------------|---------|------------------|

| July, 2024 | V1.0    | New edition      |

## **Statement**

This document is formulated and published by Geehy Semiconductor Co., Ltd. (hereinafter referred to as "Geehy"). The contents in this document are protected by laws and regulations of trademark, copyright and software copyright. Geehy reserves the right to make corrections and modifications to this document at any time. Read this document carefully before using Geehy products. Once you use the Geehy product, it means that you (hereinafter referred to as the "users") have known and accepted all the contents of this document. Users shall use the Geehy product in accordance with relevant laws and regulations and the requirements of this document.

#### 1. Ownership

This document can only be used in connection with the corresponding chip products or software products provided by Geehy. Without the prior permission of Geehy, no unit or individual may copy, transcribe, modify, edit or disseminate all or part of the contents of this document for any reason or in any form.

The "极海" or "Geehy" words or graphics with "®" or "TM" in this document are trademarks of Geehy. Other product or service names displayed on Geehy products are the property of their respective owners.

### 2. No Intellectual Property License

Geehy owns all rights, ownership and intellectual property rights involved in this document.

Geehy shall not be deemed to grant the license or right of any intellectual property to users explicitly or implicitly due to the sale or distribution of Geehy products or this document.

If any third party's products, services or intellectual property are involved in this document, it shall not be deemed that Geehy authorizes users to use the aforesaid third party's products, services or intellectual property. Any information regarding the application of the product, Geehy hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party, unless otherwise agreed in sales order or sales contract.

#### 3. Version Update

Users can obtain the latest document of the corresponding models when ordering Geehy products.

If the contents in this document are inconsistent with Geehy products, the agreement in the sales order or the sales contract shall prevail.

#### 4. Information Reliability

The relevant data in this document are obtained from batch test by Geehy Laboratory or cooperative third-party testing organization. However, clerical errors in correction or errors caused by differences in testing environment may occur inevitably. Therefore, users should understand that Geehy does not bear any responsibility for such errors that may occur in this document. The relevant data in this document are only used to guide users as performance parameter reference and do not constitute Geehy's guarantee for any product performance.

Users shall select appropriate Geehy products according to their own needs, and effectively verify and test the applicability of Geehy products to confirm that Geehy products meet their own needs, corresponding standards, safety or other reliability requirements. If losses are caused to users due to user's failure to fully verify and test Geehy products, Geehy will not bear any responsibility.

### 5. Legality

USERS SHALL ABIDE BY ALL APPLICABLE LOCAL LAWS AND REGULATIONS WHEN USING THIS DOCUMENT AND THE MATCHING GEEHY PRODUCTS. USERS SHALL UNDERSTAND THAT THE PRODUCTS MAY BE RESTRICTED BY THE EXPORT, RE-EXPORT OR OTHER LAWS OF THE COUNTRIES OF THE PRODUCTS SUPPLIERS, GEEHY, GEEHY DISTRIBUTORS AND USERS. USERS (ON BEHALF OR ITSELF, SUBSIDIARIES AND AFFILIATED ENTERPRISES) SHALL AGREE AND PROMISE TO ABIDE BY ALL APPLICABLE LAWS AND REGULATIONS ON THE EXPORT AND RE-EXPORT OF GEEHY PRODUCTS AND/OR TECHNOLOGIES AND DIRECT PRODUCTS.

### 6. Disclaimer of Warranty

THIS DOCUMENT IS PROVIDED BY GEEHY "AS IS" AND THERE IS NO WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT

LIMITED TO, THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, TO THE EXTENT PERMITTED BY APPLICABLE LAW.

GEEHY'S PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED FOR USE AS CRITICAL COMPONENTS IN MILITARY, LIFE-SUPPORT, POLLUTION CONTROL, OR HAZARDOUS SUBSTANCES MANAGEMENT SYSTEMS, NOR WHERE FAILURE COULD RESULT IN INJURY, DEATH, PROPERTY OR ENVIRONMENTAL DAMAGE.

IF THE PRODUCT IS NOT LABELED AS "AUTOMOTIVE GRADE," IT SHOULD NOT BE CONSIDERED SUITABLE FOR AUTOMOTIVE APPLICATIONS. GEEHY ASSUMES NO LIABILITY FOR THE USE BEYOND ITS SPECIFICATIONS OR GUIDELINES.

THE USER SHOULD ENSURE THAT THE APPLICATION OF THE PRODUCTS COMPLIES WITH ALL RELEVANT STANDARDS, INCLUDING BUT NOT LIMITED TO SAFETY, INFORMATION SECURITY, AND ENVIRONMENTAL REQUIREMENTS. THE USER ASSUMES FULL RESPONSIBILITY FOR THE SELECTION AND USE OF GEEHY PRODUCTS, GEEHY WILL BEAR NO RESPONSIBILITY FOR ANY DISPUTES ARISING FROM THE SUBSEQUENT DESIGN OR USE BY USERS.

#### 7. Limitation of Liability

IN NO EVENT, UNLESS REQUIRED BY APPLICABLE LAW OR AGREED TO IN WRITING WILL GEEHY OR ANY OTHER PARTY WHO PROVIDES THE DOCUMENT AND PRODUCTS "AS IS", BE LIABLE FOR DAMAGES, INCLUDING ANY GENERAL, SPECIAL, DIRECT, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OR INABILITY TO USE THE DOCUMENT AND PRODUCTS (INCLUDING BUT NOT LIMITED TO LOSSES OF DATA OR DATA BEING RENDERED INACCURATE OR LOSSES SUSTAINED BY USERS OR THIRD PARTIES). THIS COVERS POTENTIAL DAMAGES TO PERSONAL SAFETY, PROPERTY, OR THE ENVIRONMENT, FOR WHICH GEEHY WILL NOT BE RESPONSIBLE.

### 8. Scope of Application

The information in this document replaces the information provided in all previous versions of the document.

© 2024 Geehy Semiconductor Co., Ltd. - All Rights Reserved